電容的一般類型和應用分析

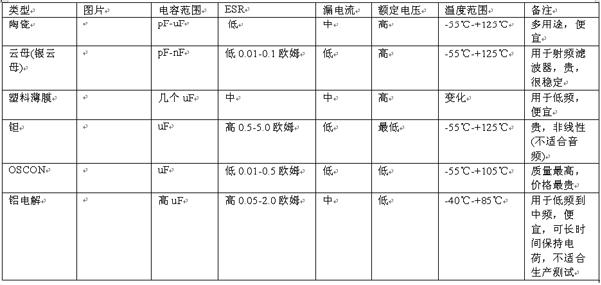

大電容可作為低頻和大電流電路的旁路,而小電容則作為高頻旁路。等效電路的模型將會隨不同的封裝類型而改變。其中主要的是等效串聯電感(ESL)。封裝越小,串聯寄生參數就越小。在一些寬頻系統中,需要並聯多個電容。旁路電容必須盡可能地靠近電源接腳。電容的另一端需要透過過孔或者寬地線連接到地平面,以保持低阻抗。電容的材料和結構將決定其特性,例如寄生特性、溫度穩定性、最大電壓、線性度、成本和尺寸。表1列舉了各種最常用的表面黏著電容。

陶瓷電容是最常見的電容類型,原因是便宜,容量範圍寬,可以提供可靠的性能。鉭電容、Oscan以及鋁電解電容都是有極性電容,特別適合作為旁路電容。鉭電容的應用範圍是低壓系統。鋁電解是從低頻到中頻系統的常規選擇,但不適合開關電路(這種電容的電荷保持性能太好了,不適合週期快速的生產測試)。Oscan是一種特殊的電容,它的寄生參數小,頻率範圍寬,溫度範圍廣,品質最好,價錢也最高。如果你有足夠預算,這種電容可為任何電路提供高品質的旁路。另外還有雲母和塑料薄膜電容。他們主要用於濾波器設計而不是旁路。由於陶瓷電容被最廣泛地作為旁路電容,討論一下如何進行選購將是很有意義的。和所期望的那樣,陶瓷電容具有寬範圍的容值和各種封裝。在這些參數中,還需要進一步選擇,才能確定最終的價格。在最新的材料清單中,電容被標誌為‘X7R’。這裡,X和7標誌著最寬的溫度範圍。最後的字母R代表電容在整個溫度範圍上的容差。該例中,電容在整個溫度範圍上的變化量僅為15%。寬溫度範圍和嚴格的容差意味著高價

格。

選擇旁路電容的封裝

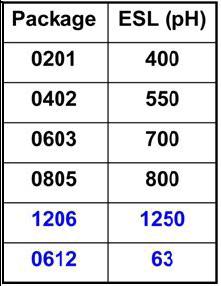

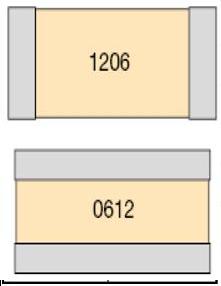

一旦電介質材料、電介質品質、溫度範圍、可接受的漏電流以及電壓範圍都滿足後,最後的選擇就剩下封裝尺寸了。通常,封裝尺寸的選擇依據是:‘上次用的是什麼’,或者是否足夠大到適合手工焊接(如果是原型設計)。需要記住的是,等效電路的模型將會隨不同的封裝類型而改變。其中主要的是等效串聯電感(ESL)。很顯然,只要電容值保持恒定,這種電容的結構就是恒定的。但如果對於同樣的電容有許多封裝類型,那麼位於極板和外層封裝之間的連接必定改變。這會帶來額外的串聯電阻和電感。封裝越小,串聯寄生參數就越小。為了證實這一趨勢,請參見圖3。正如期望的那樣,等效串聯電感將隨著封裝尺寸的減小而不斷縮減。特別注意圖 1中的1206和0612例子。

儘管他們的佔位面積相同,1206的焊接點在兩端,而0612的焊接點在兩個長邊。這只是方向上的簡單變化,卻使封裝的內部連接小了許多。令人欣喜的是,ESL降低了95%。在高頻寬電路中,串聯電感值決定了旁路電路為電源接腳提供低阻抗的能力上限。有關這點將在下節中進一步介紹。

表1:常見電容的指標和分析。

表2:陶瓷電容的分類。 表2:陶瓷電容的分類。

表3:表面黏著封裝及其等效串聯電感。 表3:表面黏著封裝及其等效串聯電感。

圖1:1206和0612兩種表面黏著封裝例子。 圖1:1206和0612兩種表面黏著封裝例子。

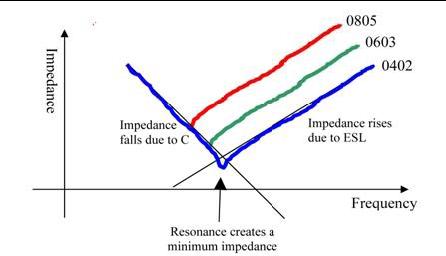

圖2:實際(非理想)電容的阻抗特性。 圖2:實際(非理想)電容的阻抗特性。

圖3:不同表面黏著封裝的實際(非理想)電容阻抗。

確定旁路電容值

通常旁路電容的值都是依慣例或典型值來選取的。例如,常用的容值是1μF和0.1μF。簡單的說,大電容作為低頻和大電流電路的旁路,而小電容作為高頻旁路。採用多個電容源於與實際電容相關的寄生參數。圖2為一個實際電容的阻抗特性。

坐標軸上沒有具體數據,其數值可以透過縮放適合任何電容。曲線的左半部份代表傳統(和理想的)電容響應:隨著頻率的增加,電容的阻抗減少。這正是想要的特性,這是因為旁路電容為電源線上的交流訊號提供了一個低阻抗迴路(等效短路)。曲線的負斜率是常數,但橫向位置取決於電容的大小。例如電容變大時,曲線的左半部份將向頻率的低階(向坐標軸左側)行動。

電容封裝中的任何電感都將引起正斜率,如圖中的右半部份所示。在這一頻率範圍內,電感先被抵銷,然後又主導了電容提供的低阻抗。由於阻抗與旁路電容的大小和構造有關,頻率響應也因此與這些因素有關,如圖3所示。因此需要仔細閱讀數據手冊,確保可以選購到合適的旁路電容封裝,這種封裝應能在目前系統工作頻率下提供低阻抗性能。請記住, 表4所列的ESL範圍為幾百pH。只有當系統頻率高於100MHz時對阻抗的影響才會越來越大。高頻寬系統的旁路

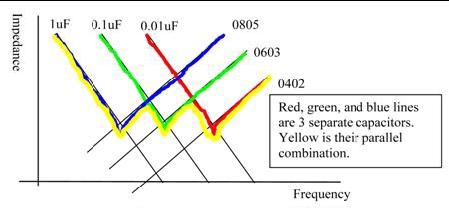

在一些寬頻系統中,用一只單電容旁路是不夠的。因為有多個頻率耦合到電源線上,旁路網路必須為寬範圍的頻率提供低阻抗。由於阻抗曲線的斜率具有實體限制,既有負的也有正的,故需要並聯多個電容。當然,在選擇每個電容的封裝類型時必須謹慎。通常BOM表中會規定所有的被動元件都要選用相同的尺寸,如都用0805電容。圖4為三只電容並聯後的阻抗與頻率關係。

圖4:三只採用相同表面黏著封裝的電容並聯阻抗。

由於每只電容採用相同的封裝,故它們的高頻響應相同。於是,這就否定了更小電容的採用!相反,封裝尺寸應該

隨同電容值一起微縮,見圖5。

圖5:三只採用不同表面黏著封裝的電容並聯阻抗。

當然,上述細節暗示著必須對旁路電容的佈局予以密切關注。任何走線長度的增加都將提高旁路路徑上的阻抗。每條走線都會貢獻單位長度上的阻抗,線越長,旁路路徑上的有用頻率就越低(相當於將圖2中的曲線左移)。因此,旁路電容必須盡可能地靠近電源接腳。電容的另一端需要透過過孔或者寬地線連接到地平面,以保持低阻抗。

作者:Mike Wong

應用工程部副總裁

Tamara Schmitz

首席應用工程師

Intersil公司

|