|

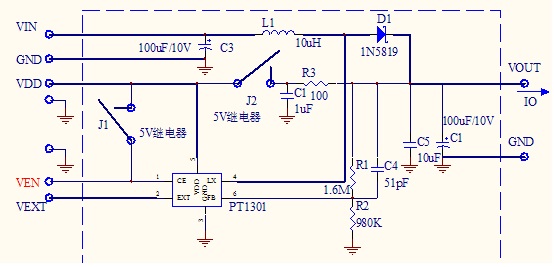

浅谈如何消除各测试项目之间的干扰 摘要:本文主要阐述了对测试项目产生干扰的一些因素 关键词:干扰 测试顺序 测试外围 随着电子产业的飞速发展,测试产品的种类越来越多,测试要求和测试精度都相应提高。有很多因素都会影响到我们测试的稳定性和精确性。如外围元器件放置的远近,元器件的种类,测试项目的前后顺序,系统地和产品地之间的压差等等。今天就我在调试产品的过程中发现的问题简单的谈一下如何消除各测试项之间的干扰。 我就以我在调试华润矽威的PT1301中碰到的问题来谈一下。此产品为DC-DC的升压转换器,其对外围元器件的要求很高,要求外部元器件与芯片距离越小越好,连线越短越好,输入输出端的电容与芯片要尽可能的近,GND端应充分接地,否则芯片内部的零电位会随开关电流而变化,造成工作状态不稳定。在测试IOFF—Shutdown Current (Vin=4.5V,Vdd=3.3V,Vo悬空,Ven=GND,EXT悬空时测量VDD Pin的输入电流)和Iswithoff-Swith off Current( Vin=6V,Vdd=3.3V,Io=1mA,Ven=3.3,EXT悬空时测量VDD Pin的输入电流)时对其他的测试项目影响很大。即第一次测试时所有测试项目均PASS,连续测试几遍的话就对其他项目影响很大,而且成不规则的各项Fail。而单独测试此两项为pass,屏蔽此两项后其他的测试项目也很稳定。测试完此两项后对所用的各个源放电,断开所有的继电器,增加delay时间,断开所有的FORCE SENSE还是没有任何起色,询问客户亦得不到什么帮助。后进行多方面的尝试,发现 Vout端对地有10uF和100uF两个电容,若将10uF的电容去掉的话,测试所有项目将OK,且连续测试也很稳定。由此得出可能是此两项参数测试完毕以后,Vout端的电容放电还未完全导致。与客户沟通后决定10uF的电容串连一个继电器来控制,测此两项电流时继电器断开,测试其他项目时将继电器闭合即可。另在测试EN Pin Level时(Vin=1.5V,VDD=3.3V,IO=1mA),调整CE Pin的电压,同时测量VO,需要满足两种情况,当VEN=1.2V,VO在正常规格范围内,当VEN=0.4V时,VO<1.5V。开始我们是按照测试规范测试VEN为高电平的情况,后测试VEN低电平的情况,发现测低电平情况下要delay 超过 200mS才可以測到稳定正常的值,而单独测试此项则只需要delay 10mS左右。究其原因发现是当VEN为高电平时测试其Vout值后芯片没有回复到初始工作状态所致,芯片要回复到原始状态需要比较长的时间,所以主要将VEN为低电平的情况放到高电平之前先测试的芯片不工作的情况,再测芯片工作的情况即可,节省了很多的测试时间。 我们在调试过程中会发现很多测试项目之间都有或多或少的联系,根据芯片的性能与测试项目之间的联系合理安排测试的顺序,合理安排测试方法,对外围元器件的布局合理分配是提高我们测试准确性和稳定性的关键,对测试效率的提高也有很大的帮助。  |